如何在cst中进行hspice仿真-和记娱乐怡情博娱188

cst的电路是支持ibis和spice模型的,这个大家都知道。但是,spice模型仅限于控制符为.subckt,就是黑盒子式的子电路模型。这期我们看看更多的未直接支持的情况,比如hspice。

hspice的输入是一个.sp文件,包含电路的线路信息“netlist”,也叫input netlist file或spice netlist。

举个传输线仿真的hspice例子:

* stripline circuit

.tran 50ps 7.5ns

.option post probe

vin 1 0 pwl 0 0v 250ps 0v 350ps 3.3v

rsource 1 2 50

tfirst 2 0 3 0 zo=50 td=0.17ns

c2 3 0 2p

tsecond 3 0 4 0 zo=50 td=500ps

rtermination 4 0 50

.probe v(1) v(2) v(3) v(4)

.end

注意,这个.sp案例中的控制符是.option,其他可能用到的控制符包括.tran,.param, .inc, .lib,.model. 等等。我们在每一句后面加上解释:

* stripline circuit 带星的是信息, comment而已

.tran 50ps 7.5ns 瞬态仿真7.5纳秒

.option post probe 控制部分:开始

vin 1 0 pwl 0 0v 250ps 0v 350ps 3.3v vin是个线性电压源,位于线路节点1和0(地)之间,t=0时 v=0v, t=250皮秒时,v=0v,t=350皮秒时,v=3.3v。pwl是piecewise linear source, 就是不同时间段不同信号。

rsource 1 2 50 节点1和2之间的内阻50

tfirst 2 0 3 0 zo=50 td=0.17ns 节点2和3之间传输线,阻抗50欧,延时0.17ns;

c2 3 0 2p 节点3和地之间的电容c2;

tsecond 3 0 4 0 zo=50 td=500ps 又一个传输线;

rtermination 4 0 50 负载阻抗50欧

.probe v(1) v(2) v(3) v(4) 在四个线路节点1234放探针

.end 结束

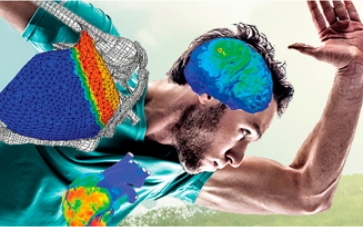

然后我们想一想这个电路如果画出来应该是什么样的?用cst的电路模块画大概是这样的(示意拓扑而已):

如果把这个.sp文件拖拽到cst中,则报错“subcircuit not found”,也就是我们刚才说的,目前cst只支持子电路,而这个hspice是包含仿真设置的文件,并不是个单纯子电路。

那么问题来了,我们如何将这个.sp文件拆成子电路和仿真设置,然后用在cst的电路仿真呢?答案是用到spice分割宏工具:

browse选中.sp文件,定义想要提取的子电路节点(可以很多个):

这里的circuit negative filter是负过滤,意思是我们不让subcircuit包括某些toplevel的内容,一般都是电压源,电流源,内阻。

这样就把hspice拆成了控制文档和电路文档两部分了,还有个log:

运行宏的cst电路中自动导入了这个子电路spice,自动添加了tran瞬态任务,自动选好“hspice导出“的仿真模式:

拆分的几部分spice内容:

有人可能问了,这不是已经导出spice了吗?为什么还要tran任务hspice export?这是因为用户可以在cst这里继续添加其他电路部分,或者3d仿真部分,然后整体再作为hspice模型导出。举个例子:

随便激励个信号(比如高斯),就导出hspice了,位置是项目文件夹->results->ds,打开查看:

可见hspice中,我们生成的option内容更多,subckt也更多,有端口信息,也有端口激励的信号(高斯signal),然后就可以拿去做hspice仿真了。

最后一点,如果cst与其他hspice仿真工具都有安装在同一台机器,可以用下面这个宏工具明确hspice.exe的位置,这样tran任务中就会出现新的选项,可以直接调用hspice仿真工具仿真并返回结果,免去以上hspice分割和导出sp文档的步骤哦!

小结:

1. cst虽然不能直接仿真hspice,但是可以处理hspice,拆成子电路仿真;还可以配合三维电磁仿真,场路结合,电路任务,最后导出新系统的hspice。

2. 拆出来的或导出新的hspice可以直接或间接地在其他hspice仿真工具中使用。

3. spice拆分宏工具也适用于pspice,ltspice,支持其他spice后缀,*.cir;*.net; *.txt",可多次使用。

4. 常见场景是ddr供应商提供hspice用来si仿真。

5. knowledge base faq原文:qa00000071096

(内容、图片来源:cst仿真专家之路公众号,侵删)

和记娱乐怡情博娱188的版权与免责声明:

凡未注明作者、来源的内容均为转载稿,如出现和记娱乐怡情博娱188的版权问题,请及时联系和记娱乐怡情博娱188处理。我们对页面中展示内容的真实性、准确性和合法性均不承担任何法律责任。如内容信息对您产生影响,请及时联系和记娱乐怡情博娱188修改或删除。

-

2023-12-29

-

2023-12-29

-

2023-12-29

-

2023-12-28

-

2023-12-28

-

2023-12-28

-

2023-12-27

-

2023-12-27

-

2023-12-27

-

2023-12-26

-

[abaqus] abaqus如何建模?abaqus有限元......

2023-07-07

-

2023-08-24

-

[abaqus] 关于2013版的thinkdesign用......

2014-06-20

-

2017-05-19

-

[abaqus] thinkdesign技术在创新设计中的......

2015-03-03

-

[abaqus] 基于thinkdesign回弹补偿功能的......

2015-03-03

-

[abaqus] td styling之眼镜三维建模、渲染......

2015-03-03

-

2015-03-03

-

2023-08-29

-

2015-03-03

-

[有限元知识] abaqus分析指南120:裂纹萌生与扩......

2023-12-29

-

[有限元知识] abaqus分析指南119:将内聚材料概......

2023-12-29

-

2023-12-29

-

2023-12-28

-

[有限元知识] abaqus分析指南116:多个丰富的功......

2023-12-28

-

[有限元知识] abaqus分析指南115:用水平集方法......

2023-12-27

-

[有限元知识] abaqus分析指南114:水力驱动裂缝......

2023-12-27

-

[有限元知识] abaqus分析指南113:基于内聚段法......

2023-12-26

-

[有限元知识] abaqus分析指南112:有限元方法将......

2023-12-26

-

[有限元知识] abaqus分析指南111:温度和场变量......

2023-12-26

地址: 广州市天河区天河北路663号广东省机械研究所8栋9层 电话:020-38921052 传真:020-38921345 邮箱:thinks@think-s.com

和记娱乐app官网登录 copyright © 2010-2023 广州思茂信息科技有限公司 all rights reserved. 粤icp备11003060号-2