cst电磁仿真考虑 esd 保护二极管元件的差分传输线阻抗仿真-和记娱乐怡情博娱188

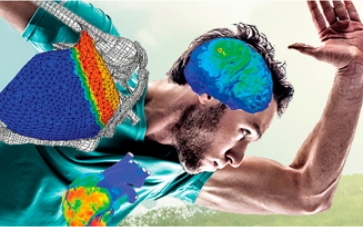

通过单根双绞线 (stp) 在发射器和接收器之间传输高带宽数据需要在发射器和接收器端使用额外的 esd(静电放电)保护元件。这些保护元件安装在印刷电路板 (pcb) 上。由于数据速率为 6 gbps,pcb 传输线的设计必须从信号完整性的角度考虑 esd 保护元件。在这篇博客文章中,我们介绍了 esd 保护元件的影响以及为保持信号完整性所需的布局优化。最后,我们展示了模拟结果与测量结果之间的比较。

*以下内容由 inova semiconductors gmbh 的应用工程师 reiner welzer 共同撰写。他在信号和电源完整性以及 rf 和模拟信号 pcb 的 emc 合规设计方面拥有 20 多年的经验。近年来,他广泛研究电子电路的 esd 保护,尤其是汽车电子电路。

耦合微带线建模

通过单根双绞线电缆传输数据,pcb 上的连接采用边缘耦合表面微带导体实现。高速数据传输大多采用差分信号。这提供了良好的电磁兼容性 (emc)。通常,使用标称线路阻抗为 100 ω 的边缘耦合表面微带导体,位于顶层。图 1 显示了用于模拟的边缘耦合微带线的尺寸,可提供 100 欧姆的差分线路阻抗。

图 1. 带尺寸的差分线模型

对于线路阻抗计算,正确的材料特性和正确的阻焊层形状建模非常重要。如图 1 所示,阻焊层建模为覆盖微带导体的薄皮。

由于差分线通过插头连接到电缆,因此插头处很可能会发生 esd 事件。此类 esd 事件会在短时间内(< 1 ns)产生非常高的电压和电流峰值,并可能损坏电子元件。为了避免这种情况,应将 esd 保护元件连接到差分线的两个导体。此类应用通常使用 tvs(瞬态电压抑制器)二极管。它们具有非常快的响应时间,可在短时间内将电压限制在某个值。

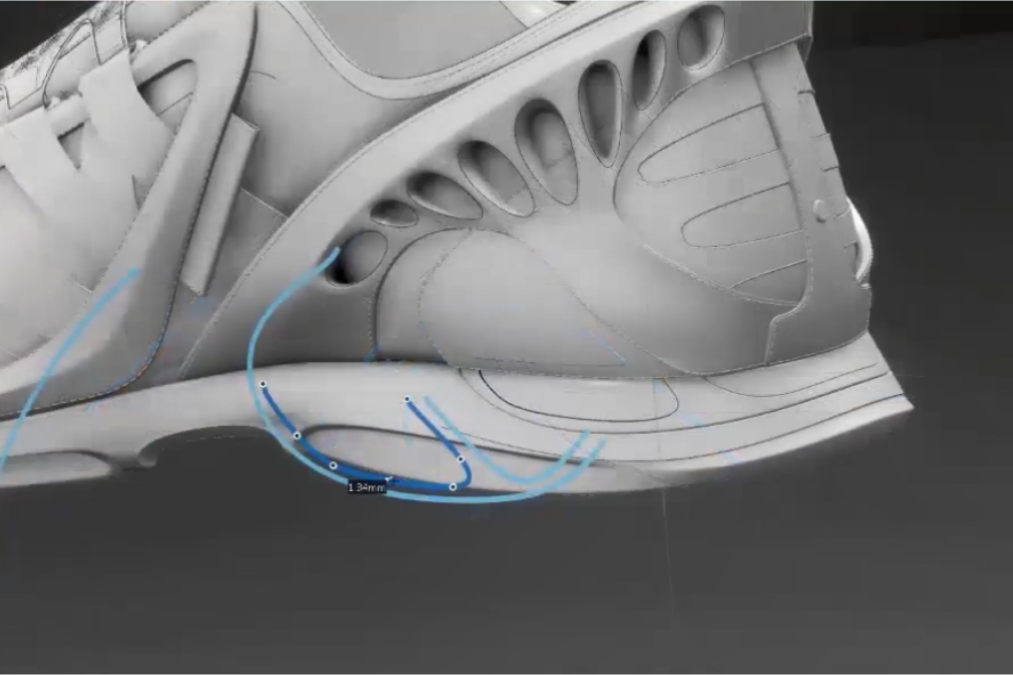

对于 6 gbps 的高速数据速率,使用具有低寄生元件的小型元件封装尺寸非常重要。对于分析的几何形状,我们使用了 nexperia [1] 的 esd 保护二极管 pesd5v0c1bls-q。该器件的最大二极管电容为 0.3 pf,封装尺寸为 1 mm x 0.6 mm x 0.47 mm。在仿真中,esd 二极管使用“集总元件”定义。它们仅通过其寄生电容再现。“集总元件”是 cst 内部元件,可以表示 r、l、c 元件。图 2 显示了包括 esd 二极管在内的差分线的仿真模型。

图 2. 带有 esd 二极管的差分线仿真模型

在图 2 中,可以看到差分信号线上 esd 元件的接地焊盘比走线更宽。显然,此特定位置的横截面变化会导致线路阻抗变化。根据阻抗变化的大小,会对信号完整性产生影响。

布局前 tdr 仿真

分析传输线沿线阻抗的一种著名方法是时域反射法 (tdr)。其工作原理类似于雷达原理,即发射脉冲并在输入端记录反射信号。通过评估反射信号可以获得有关阻抗曲线的信息。cst studio suite还可以使用时域或频域求解器执行 tdr 仿真。对于此布局前调查,我们使用频域求解器。这是合理的,因为离散化结构相对简单,并且与波长相比尺寸较小。由于频域求解器仅提供 s 参数结果,我们通过后处理回波损耗 s 参数 s 11来计算 tdr 结果. 以高斯信号作为输入信号,可以根据回波损耗信息重建输出信号。我们通过应用公式 1 来计算 tdr。

仿真中定义的最大频率范围为8.4 ghz,对应10%-90%的上升时间为104 ps。

图 3. 高斯脉冲的时间积分

cst studio suite 可以使用基于模板的后处理“从 s 参数进行 tdr 计算”自动执行此计算,如图 4 所示。

图 4. 基于模板的 s 参数 tdr 计算后处理

尽管二极管电容值相当小(0.3 pf),但在执行 tdr 模拟时必须考虑它。它会降低标称线路阻抗(100 ω)。图 5 说明了考虑和不考虑此电容的比较。

图 5. 有和没有二极管电容的 tdr 仿真

布局修改

设计高速数据通道时,通常设置允许的最大阻抗变化为±10%。在参考阻抗为100 ω的情况下,我们可以从图5中看到曲线下降到83 ω。这将无法满足要求的下限(90 ω)。为了满足阻抗要求,必须围绕 esd 二极管位置进行布局优化。

由于 esd 二极管电容会降低此区域的线路阻抗,因此必须通过降低传输线每米电容来补偿此影响。最有效的方法是切掉 esd 二极管下方的参考平面。可以通过模拟找到凹陷接地区域的最佳尺寸。图 6 显示了经过多次模拟迭代后,针对某一层结构修改后的参考平面的优化配置。

图 6. 带切口的参考平面(gnd 通孔不可见)

图7中可以看到相应的阻抗曲线改善。

图 7. 参考平面有切口和无切口时的阻抗比较

请注意,接地平面上的切口可能会允许来自其他开关或干扰信号的串扰。因此,建议不要将任何敏感信号线布线在此切口下方。在 pcb 布局设计工具中,可以通过创建限制/禁入区域来确保这一点。

从回波损耗 s 参数 s 11也可以看出线路阻抗的改善

(图 8)。可以观察到回波损耗改善了约 12 db。这也意味着信号完整性得到了改善。

图 8.参考平面上有切口和无切口时的回波损耗 (s 11 ) 比较

通过比较眼图结果,还可以证明凹陷参考平面的信号完整性行为更好。所使用的数字伪随机位序列 (prbs) 具有以下属性:

l伪随机数12

l差分电压电平±200mv

l上升和下降时间为 80 ps,周期长度对应于 3 ghz

图 9 和图 10 显示了两种布局的眼图。

图 9. 带有参考平面切口的眼图。

图 10. 没有切除参考平面的眼图。

测量比较

为了确认仿真结果,我们创建了一个具有优化参数(由 cst studio suite 仿真发现)的 pcb 布局。我们利用 sequid 的差分 tdr 测量系统执行了 tdr 阻抗测量。在测量过程中,传输线通过 sma 插座连接。对于仿真,无需考虑连接器,因为它们只会增加计算能力和时间,而不会影响 esd 二极管周围的线路阻抗。差分线的末端可以保持开路。

用于测量的制造的 pcb 原型是标准 fr-4 板,有 4 层,总厚度约为 1.6 毫米。差分对尺寸与布局前调查中使用的尺寸略有不同,但参考平面切口尺寸保持不变。图 11 显示了 cst studio suite 用于测量比较的 pcb 布局原型的一部分。

图 11. cst mws 内部的 pcb 原型模型。

图 12 显示了测量和模拟之间的线路阻抗结果比较。与测量的良好一致性证实了 cst mws 的模拟。

图 12. 测量和模拟之间的阻抗比较。

结论

为了传输高速数据信号,重要的是实现整个高速数据通道的平滑线路阻抗曲线。信号完整性要求通常为参考阻抗的±10%。在这篇博客文章中,我们介绍了使用 cst studio suite 对此类传输线进行 3d 布局仿真和优化。我们展示了在布局前阶段使用此仿真工具的好处,尤其是在开发时间方面。我们表明,在优化过程中尊重 esd 二极管元件(电容信息)非常重要,以获得更真实的结果。最后,模拟和测量之间的良好一致性证实了使用 cst studio suite 进行模拟结果的准确性。

参考

[1]https://www.nexperia.com/products/esd-protection-tvs-filtering-and-signal-conditioning/automotive-esd-protection-and-tvs/automotive-esd-protection/pesd5v0c1bls-q.html

[2] cst studio suite 2024 在线帮助。

-

[abaqus] 如何查看abaqus/standard 分析作业的运行状态

2024-07-05

-

2024-07-05

-

[abaqus] abaqus调整从面节点坐标造成的单元异常

2024-07-05

-

2024-07-04

-

2024-07-04

-

[abaqus] abaqus无法为模型成功划分六面体(hex)单元网格,应

2024-07-04

-

2024-07-03

-

2024-07-03

-

[abaqus] abaqus新增的自底向上网格划分技术有什么优点?有何注意

2024-07-03

-

[abaqus] abaqus划分网格时,在什么情况下需要使用分割(part

2024-07-02

-

2023-08-24

-

[abaqus] abaqus如何建模?abaqus有限元分析教程

2023-07-07

-

2023-08-29

-

[abaqus] 有限元分析软件abaqus单位在哪设置?【操作教程】

2023-09-05

-

[abaqus] 如何准确的评估真实行驶工况条件下的空气动力学性能

2020-11-19

-

[abaqus] abaqus单位对应关系及参数介绍-abaqus软件

2023-11-20

-

[abaqus] abaqus里面s11、s12和u1、u2是什么意思?s和

2023-08-30

-

[abaqus] abaqus软件教程|场变量输出历史变量输出

2023-07-18

-

2023-07-26

-

[abaqus] abaqus软件中interaction功能模块中的绑定接

2023-07-19

-

[有限元知识] 汽车座椅的热行为:利用powerflow仿真来增强热舒适度

2024-06-27

-

2024-06-07

-

[有限元知识] abaqus软件分析指南394:涉及孔隙流体压力的程序

2024-06-06

-

[有限元知识] abaqus软件分析指南393:热通量与涉及热自由度的程序

2024-06-06

-

[有限元知识] abaqus软件分析指南392:涉及机械自由度的程序

2024-06-06

-

[有限元知识] abaqus软件分析指南391:参数研究结果

2024-05-30

-

[有限元知识] abaqus软件分析指南390:参数化研究设计的生成和执行

2024-05-30

-

2024-05-30

-

[行业资讯] 可持续创新|行业首家“国家级工业设计中心”的发展秘笈

2024-05-29

-

[行业资讯] 上课啦!达索cst核心模块及emc仿真培训(深圳站)即将开

2024-05-29

地址: 广州市天河区天河北路663号广东省机械研究所8栋9层 电话:020-38921052 传真:020-38921345 邮箱:thinks@think-s.com

和记娱乐app官网登录 copyright © 2010-2023 广州思茂信息科技有限公司 all rights reserved. 粤icp备11003060号-2